HDL 베리파이어는 FPGA/ASIC의 설계를 개발하는 설계 검증 담당 엔지니어가 시뮬링크에서 UVM 컴포넌트와 테스트 벤치를 생성하면서 시놉시스(Synopsys), 케이던스(Cadence), 멘토 그래픽스(Mentor Graphics) 등과 같이 UVM을 지원하는 시뮬레이터에서 사용할 수 있도록 지원한다.

최근 윌슨리서치그룹에서 실시한 연구조사 결과에 따르면, 약 48%의 FPGA 설계 프로젝트와 약 71%의 ASIC 설계 프로젝트에서 엔지니어는 설계 검증을 위해 UVM을 사용하고 있다.

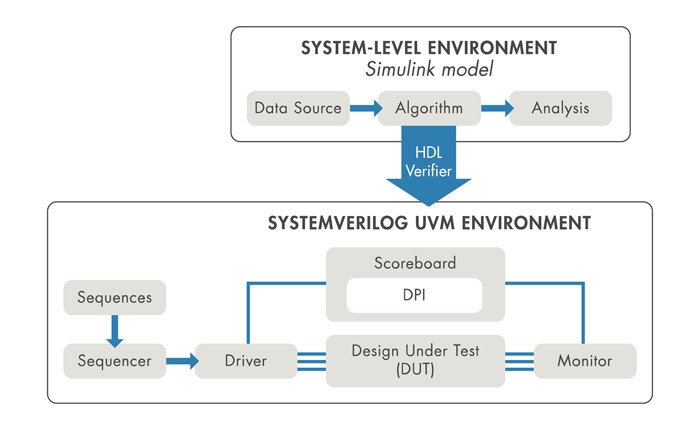

알고리즘 개발자와 시스템 설계자는 매트랩/시뮬링크를 통해 새로운 알고리즘을 개발한 후, 설계검증(DV) 엔지니어가 매트랩과 시뮬링크 모델을 참조해 RTL 테스트 벤치를 코딩하는 구조로 진행한다. 해당 기능이 업데이트되면서 UVM 컴포넌트를 자동으로 생성할 수 있게 된 셈이다.

HDL 베리파이어는 ASIC/FPGA의 프로덕션 검증을 담당하는 설계 검증 팀에 대한 기능도 업데이트됐다. 기존에 설계 검증 팀은 HDL 시뮬레이터를 통해 엄격한 테스트 벤치를 개발하기 위해 시스템베리로그에서 코드를 작성하는 수작업이 필요했으나 모델에서 직접 검증 컴포넌트를 생성할 수 있게 된다.

에릭 시간 매스웍스 수석 HDL 제품 마케팅 매니저는 “이번에 발표한 HDL 베리파이어는 기존의 매트랩/시뮬링크 모델로부터 UVM 및 시스템베리로그 DPI 컴포넌트를 생성하는 새로운 기능을 통해 DV 엔지니어의 생산성을 높이면서 엔지니어 간 협업을 향상시킬 수 있을 것으로 기대한다”고 말했다.