With Support for Platform Security Architecture Trusted Firmware-M from ARM

Cypress Semiconductor Corp. announced availability of the Platform Security Architecture(PSA) Trusted Firmware-M reference example from ARM for its PSoC 6 microcontrollers(MCUs), enabling a solution that adheres to the highest level of protection as defined by PSA.

By leveraging PSA's holistic set of threat models, security analyses, hardware and firmware architecture specifications, and Trusted Firmware-M reference implementation, Internet of Things(IoT) designers can quickly and easily implement secure designs with PSoC 6 MCUs.

“Connected devices are being deployed at a rapid pace, and to truly realize the benefits of these technologies, security cannot be optional,” said Paul Williamson, vice president and general manager, IoT Device IP Line of Business, ARM.

“Enabling secure MCU development across the breadth of IoT applications is a shared industry responsibility, and Cypress' PSoC 6 MCUs will further extend the benefits of PSA to our ecosystem.”

“As a direct result of the security features built into PSoC 6 MCUs and our collaboration with ARM, we have been able to quickly offer support for Trusted Firmware-M,” said Sudhir Gopalswamy, senior vice president of the Microcontrollers and Connectivity Division at Cypress.

“We're excited to offer designers a secure solution that is ultra-low power, flexible and adheres to PSA principles.”

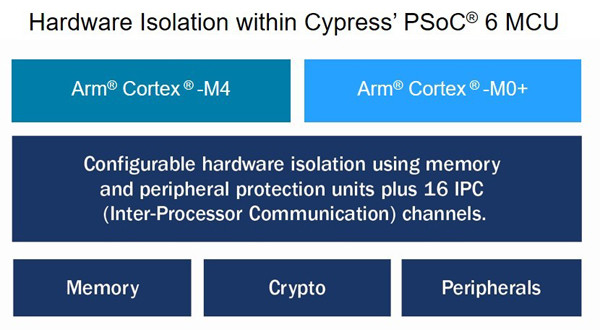

Cypress' PSoC 6 MCUs achieve the highest level of protection defined by the PSA using dual ARM Cortex-M cores combined with configurable memory and peripheral protection units.

The MCUs provide three levels of hardware-based isolation. An isolated execution environment for trusted applications using a dedicated ARM Cortex-M0+ core, secure element functionality that hosts root of trust operations and system services, and isolation for each trusted application.

These three levels of isolation together reduce the attack surface for threats. The system is augmented with a true random number generator(TRNG) and cryptographic accelerators, while the Cortex-M4 core in the PSoC 6 MCU architecture delivers a clean programming model for the rich execution environment for unsecure applications.