![[source=pixabay]](https://cdn.itbiznews.com/news/photo/202010/22425_19781_352.jpg)

특성화 작업 전에 먼저 클럭, 스트로브, 데이터 및 명령과 같은 관심 대상 신호에 대한 액세스 권한을 확보해야 한다. 사용 가능한 바이어스가 있는 경우, DRAM에서 직접 탐색할 수 있으므로 이러한 신호를 액세스하기에 가장 좋은 곳이 바로 바이어스라고 할 수 있다.

하지만 바이어스 액세스는 제한적이며, 특히 가능한 한 볼륨을 줄이기 위해 보드에 여러 개의 디바이스가 로드된 경우에는 더 제한이 심하다. 다음 옵션은 BGA 인터포저를 사용하는 것입니다. 인터포저는 테스트 대상인 모든 신호의 경로를 지정한다.

인터포저는 BGA 리워크 스테이션을 사용해서 보드에 납땜되며 DRAM은 BGA 리워크 스테이션을 사용해서 인터포저에 납땜된다. 오실로스코프와의 연결을 위해서는 ZIF 또는 마이크로 프로브 헤드가 사용된다.

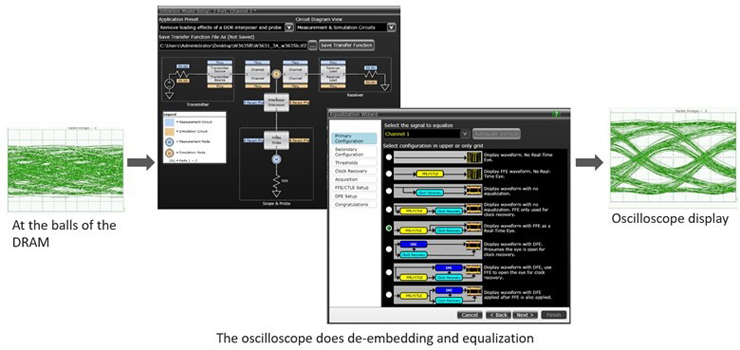

인터포저를 로드할 때 버스를 파괴하지 않는 것이 매우 중요하다. 설계자는 최소한의 부하로 신호 속도를 처리할 수 있게 인터포저가 설계되도록 주의해야 한다. 인터포저가 버스를 파괴하지 않더라도 신호를 디임베딩해야 한다.

디임베딩 소프트웨어의 S 파라미터를 사용하여 신호의 주파수 응답을 수정하는 전송 함수 파일을 만드는 데, 여기에서 3000MT/s 이상의 더 빠른 데이터 전송 속도에서는 기호 간 간섭으로 인해 DRAM에서의 아이 수축이 예상된다.

DDR5는 수신기에 의해 래칭된 후 데이터 아이를 개선하기 위해 결정 피드백 이퀄라이제이션과 같은 이퀄라이제이션이 필요할 수 있다. 사용된 이퀄라이제이션 방법은 반사로 인한 노이즈 증폭 없이 아이를 열 수 있어야 한다.

DDR5에서는 데이터 마진은 점점 줄어들고 있음을 확인할 수 있다. 즉, 클럭이나 스트로브, 데이터, 전압 요건 등의 주요 신호 간 타이밍이 충족될 수 있도록 타이밍과 신호 무결성의 특성화를 수행해야 한다. LPDDR4에서 JEDEC는 DRAM에 쓰기 사이클 타이밍을 측정하는 tDQS2DQ 테스트를 도입했다.

테스트 결과 DRAM 설계자는 컨트롤러가 DRAM에서의 막대한 차이를 다룰 필요가 없도록 하기 위해 컨트롤러에서 어느 정도의 스큐를 허용하는지 파악할 수 있다.

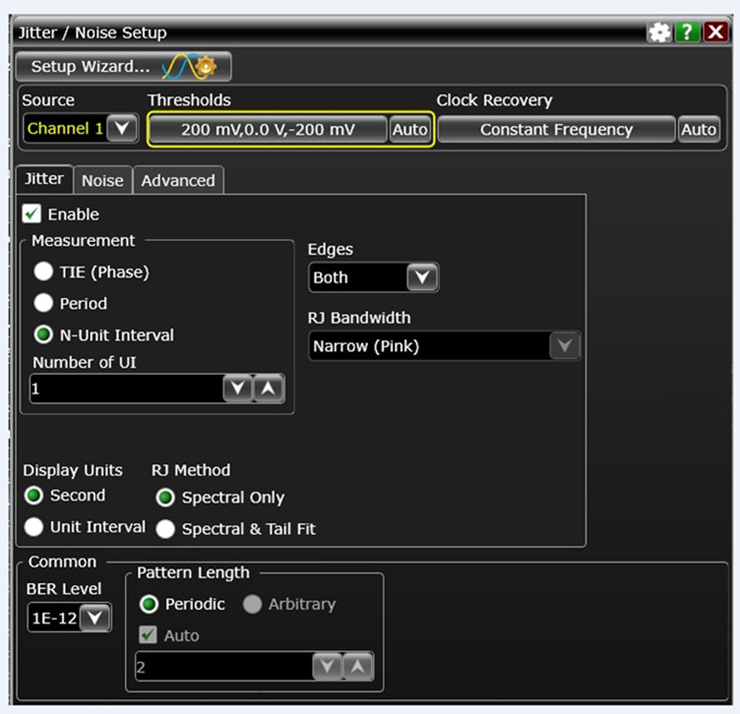

보다 중요한 DRAM 컴플라이언스 테스트 중 하나로써 이 또한 DDR5에도 중요하다. 지터 특성화의 경우 랜덤 및 결정적 지터 구성 요소를 구분할 수 있어야 한다(그림 2).

이러한 구분이 가능하면 설계자가 잠재적인 노이즈, 크로스톡 또는 듀티 사이클 왜곡과 같은 문제의 출처를 파악할 수 있다. 데이터 아이 테스트는 데이터 유효 기간을 검증하는 데 사용되는 표준 모델이다.

데이터 아이 테스트는 아이 높이와 아이 너비 측정을 수행한다. 아이가 닫힌 경우, 이퀄라이제이션 방법을 사용해서 아이를 열어야 하며, 아이 너비와 아이 높이 측정 시 계측기 노이즈를 고려해야 한다. 지터 측정 시에도 마찬가지다.

DDR5 설계는 복잡하기 때문에 시뮬레이션, 분석, 디버깅 및 컴플라이언스 테스트를 포함하는 설계 사이클이 수반되어야 한다. 설계 워크플로는 시뮬레이션, 실험 설계 및 컴플라이언스 간 측정 상관관계를 파악할 수 있는 데이터 분석 기능을 갖추고 있어야 한다.

최신 시뮬레이션 도구를 사용하면 실제 디바이스를 테스트에 사용하기 전에 조기 테스트를 위해 컴플라이언스 테스트 소프트웨어에 사용될 파형 파일을 생성할 수 있다.

테스트가 실패할 경우, 데이터 분석 도구로 최적화 지점을 찾는 방식으로 조기 재설계 또는 최적화 작업을 수행할 수 있다.

그 다음 실제 디바이스 테스트 시, 측정 상관 관계를 파악하여 설계 성능과 마진을 추가로 미세 조정할 수 있다.

DDR5 송신기 테스트의 성공 여부는 측정에 어떤 도구를 사용하는지에 달려 있다고 해도 과언이 아니다. 완벽한 DDR5 송신기 솔루션은 프로브, 오실로스코프, 컴플라이언스 또는 검증 소프트웨어로 구성되어 테스트 속도와 테스트 파라미터를 모두 다룰 수 있어야 한다.

오실로스코프를 선택할 때에는 지터 및 노이즈 성능이 가장 낮은지 확인해야 한다. 컴플라이언스 또는 검증 작업에서 상호운영성과 반복성을 보장하기 위해 자동화된 소프트웨어 패키지를 사용하는 경우도 있기 때문이다.

오실로스코프를 사용해서 수동으로 측정할 수 있지만, 테스트 파라미터를 측정 단계로 변환하는 작업은 테스트 시간이 길어지게 만드는 요인이 되기에 주의해야 한다.

글 : 에일리 그룸바인(Ailee Grumbine) / 전략 제품 플래너 / 키사이트테크놀로지스

관련기사

- 차세대 메모리 DDR5 검증을 위한 송신기 테스트의 영향 이해하기 ①

- [그것을 알려주마] “AMD-자일링스(Xilinx) 인수합병, 경쟁자는 진짜 인텔(Intel)인가?”

- 세계 최초 DDR5 D램 출시한 SK하이닉스, “서버시장 리더십 확대”

- 하반기 서버·모바일용 D램 가격 약세…그래픽 D램 일부 상승세 전망

- 키사이트, 양자컴퓨팅 스타트업 ‘래버퀀텀’ 인수…양자 엔지니어링 툴셋 고도화

- 게이밍·그래픽카드용 D램, 올해부터 GDDR6가 ‘대세’

- 키사이트, 8채널 동시 측정 가능한 오실로스코프 ‘인피니엄 MXR’ 발표

- 로데슈바르즈, AESA 레이더 초정밀 테스팅 제품군 발표

- 키사이트, 테스팅·측정기술 지원 서비스 강화…키사이트케어 확장

- 로데슈바르즈, 26.5GHz 주파수 지원 ‘휴대용 벡터 네트워크 분석기’ 출시