![[사진=게티이미지뱅크]](https://cdn.itbiznews.com/news/photo/202107/42739_38391_3130.jpg)

반도체 산업은 전환점에 직면했다. 사물인터넷(IoT), 빅데이터, 인공지능(AI)이 몰고온 변화 덕분에 반도체 수요는 그 어느 때보다 높다.

이와 동시에 전통적인 무어의법칙에 따른 2D 스케일링 기술로는 반도체 제조사들이 더 이상 PPACt(전력/성능/공간비용/출시소요기간)를 지속적으로 개선할 수 없다. 이는 전자제품에서 주요 프로세스 엔진 역할을 하고, 전력 효율과 성능이 중요한 ‘로직 칩’에서 더 두드러지게 나타난다.

어플라이드머티어리얼즈(AMAT)는 최근 온라인 ‘로직 마스터 클래스’를 열고 로직 스케일링의 로드맵 및 당면 과제, PPACt의 지속적인 향상은 물론 트랜지스터와 인터커넥트 스케일링, 패터닝, 설계 기술 공동최적화(Design Technology Co-Optimization, DTCO) 등 여러 분야에 대해 논의한 바 있다.

이러한 분야의 공통점은 칩 아키텍처, 새로운 3D 구조, 신소재, 소형화 방법, 첨단 패키징을 포함한 칩 연결 등 다양한 방법을 병행해 2D 스케일링을 보완해야 한다는 것이다.

로직 마스터 클래스에서 논의된 주제 중에서도 트랜지스터 설계와 첨단 로직 스케일링을 구현하기 위해 극복해야할 물리적인 한계에 대해 이 글에서 살펴보고자 한다.

트랜지스터 스위칭 속도와 변동성

트랜지스터는 스위치처럼 작동한다. 최상의 성능을 구현하려면 드라이브 전류를 최대화하고 커패시턴스(capacitance) 저항을 낮춰 스위칭을 지연해야 한다.

가령 핀펫(FinFET) 트랜지스터에서는 핀 높이, 채널의 게이트 길이, 채널을 가로지르는 전자의 이동성, 스위칭 임계 전압, 스위치의 온오프 상태를 제어하는 게이트 산화물 두께 등 다양한 물리적 매개변수를 조정함으로써 속도를 향상시킨다. 활성도 높은 도펀트(dopant)를 채널 부위에 형성해 전기 저항을 낮추고 있다.

또 하나의 중요한 요소는 트랜지스터 변동성이다. 회로에서 가장 속도가 느린 트랜지스터로 인해 성능이 저하되기 때문이다. 이러한 분포도를 낮춰 변동성을 줄임으로써 회로 속도를 높일 수 있다.

핀펫 성능 장벽 설명: 핀 벤딩(Fin Bending)

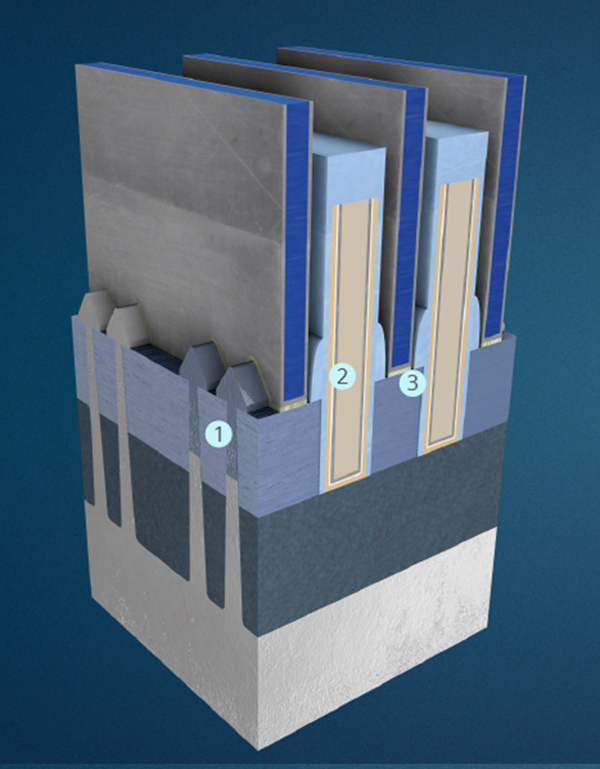

차세대 핀펫 설계에서 가장 시급한 과제를 짚어보자. 핀펫 구조는 ▲채널과 STI(Shallow Trench Isolation) ▲하이케이 메탈 게이트(High-K Metal Gate, HKMG) ▲트랜지스터 소스/드레인(Drain) 저항 모듈 등 크게 3개 모듈로 구분된다.(그림 1)

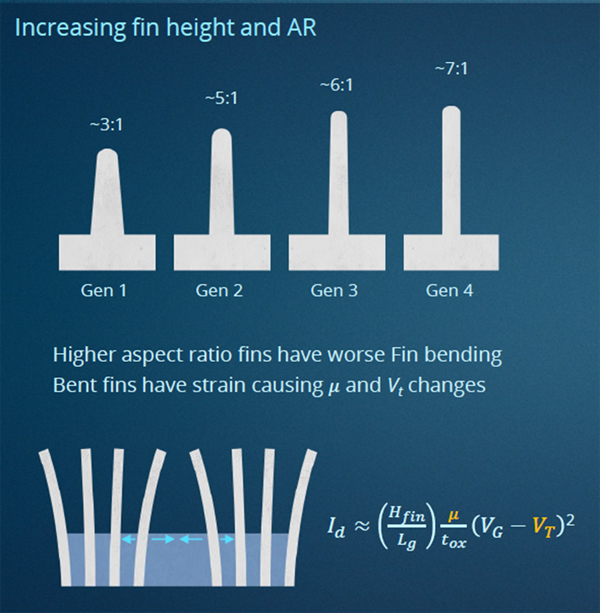

업계는 채널과 STI 모듈 분야에 대해 여러 기술 노드에 걸쳐 핀 높이를 상향하고 핀 폭을 좁히며 속도를 높여왔다. 그러나 핀 사이에 배치해야 하는 격리 산화물이 변형을 일으키면서 길고 좁은 핀들이 제조 공정 중 벤딩에 더 취약해지는 지점에 도달하고 있다.

이러한 벤딩은 전자 이동성을 저해하고 임계 전압에 영향을 주는 반발적 변형을 초래해 트랜지스터 변동성을 증가시켜(그림 2), 핀 밴딩에 대처하기 위해서는 신소재 공학 솔루션이 필요하다.

글: 마이크 샤지끄(Mike Chudzik) / 신사업그룹 / 어플라이드머티어리얼즈(AMAT)

관련기사

- TI, 마이크론 12인치 팹 인수…65나노/45나노(nm) 제품 양산확대

- 자일링스, 전자설계자동화(EDA) 툴 ‘비바도 ML 에디션’ 출시

- 신 공정시스템 공개한 AMAT, “빠른 결함 노이즈 검출로 수율 Up”

- 인텔, 美 애리조나에 팹 2기 건설…“파운드리 비즈니스 사업부 신설”

- “팹(Fab) 장비 투자액 3년 연속 성장세…파운드리·메모리가 견인”

- 美 국가안보위, “중국 반도체 개발 막을 조치 필요”…의회에 권고

- M램과 Re램, 그리고 PC램…IoT·클라우드 시대를 견인하는 차세대 메모리기술

- 차세대 메모리반도체 양산에서의 이슈, “균일성 보장하는 증착공정이 핵심”

- 버추얼랩, KICET와 소재 R&D 플랫폼 고도화 ‘맞손’…MOU 체결

- 미세공정기술의 진화…로직의 지속적인 스케일링을 위한 혁신의 중요성 ②