![[사진=게티이미지뱅크]](https://cdn.itbiznews.com/news/photo/202108/47116_42546_4943.jpg)

지난 글에 이어 이번 글에서는 계층적 DFT(Design-For-Test)가 제공하는 다양한 이점에 대해 알아보겠다.

이전 기고문 확인하기

☞ 반도체 엔지니어 주목, “DFT 자동화의 물결에 주목하라” ①

요소

계층적 DFT는 공통 플랫폼에서 작동하는 DFT 툴셋을 포함해 완전 자동화된 DFT 솔루션을 갖는다는 이점이 있다. 이는 모든 파라미터(테스트 시간, 면적 소비, 전력 소비 등) 전반에 걸쳐 일반적인 사용자 지시를 받아 스마트한 결정을 내림으로써 균형 잡힌 테스트 비용, 시간 및 커버리지를 달성할 수 있다.

DFT가 필연적으로 업스트림의 RTL로 옮겨 짐에 따라 이를 프론트엔드 설계 플로우에 통합하고, 작업을 반복 가능한 플로우에서 관리하며, 설계에 대한 이해를 유지하여 다운스트림 통합을 원활히 하는 일이 갈수록 더 중요해지고 있다.

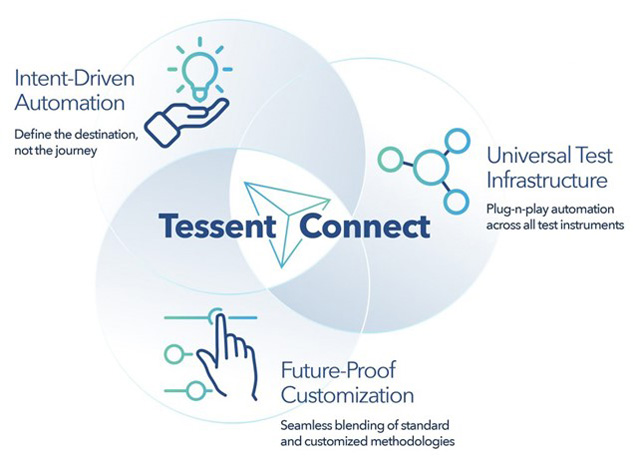

DFT 플로우에 대한 최적의 엔드투엔드 자동화를 달성하기 위한 요소는 크게 다음 세 가지 범주로 설명할 수 있다(그림 2).

- 의도 기반의 자동화

- 범용 테스트 인프라

- 미래에 대비한 맞춤화

이러한 기능을 통해 팀 간에 손쉽게 업무전달을 수행해 효율적이고 동시병행적으로 설계를 진행할 수 있다. 이는 DFT 시간을 줄이고 예측 가능성을 높여준다. 이것이 다음 프로젝트를 위한 DFT를 계획할 때 고려해야 할 기능이다.

이러한 엔드투엔드 DFT 자동화를 통해 수많은 DFT 단계의 복잡성을 줄이고 시장 진입 시점을 앞당길 수 있고, 사용자는 보다 높은 추상화 수준에서 작업할 수 있다. DFT를 삽입하고, 패턴을 생성하며 DFT 기능을 최상위 레벨에서 통합시키는 문제는 모두가 통합된 플러그-앤-플레이 환경에서 관리된다.

이러한 통합 플랫폼을 갖추지 못한 기업은 BIST와 ATPG 같은 DFT 기능을 관리하는 데 애를 먹게 되며, 코어 레벨의 DFT와 패턴을 최상위 레벨에서 통합하기 위해 많은 단계를 밟아야 한다.

의도 기반의 자동화

디자이너는 의도 기반의 자동화를 통해 상위 수준의 테스트 목표를 플로우 초기부터 DFT 툴에 기술할 수 있다. 모든 DFT 단계마다 상세한 단계별 스크립트를 작성할 필요가 없는 것이다.

예를 들면, 디자이너가 다양한 스캔 모드에 대해 ATPG 환경을 설정해야 한다고 하자. 이 경우, 일반적으로 다수의 스크립트를 작성해 해당 스크립트와 프로시저 파일을 추적한 뒤에 각 테스트 모드에 적합한 설정 파일을 로드해야 한다.

하지만 의도 기반의 자동화에서는 모든 스캔 구성(코어 내부, 외부, 바이패스 모드 등)이 한 번에 삽입되어 공통 데이터베이스에 저장된다. 그 다음 이 툴은 ATPG 단계에서 어떤 스캔 모드를 가져올 것인지만 알면 이어서 세부 정보를 처리할 수 있다.

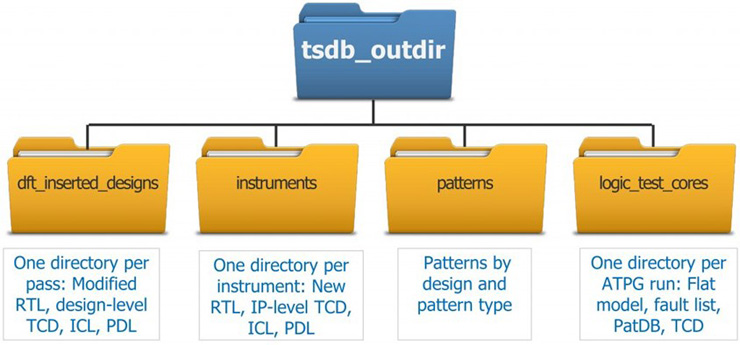

모든 DFT 툴을 공통 데이터베이스 상에 갖추는 것이 플로우의 유용성 측면에서 매우 중요해지고 있다. 이 새로운 자동화를 통해 모든 데이터와 생성된 파일이 데이터베이스 내에서 계층적으로 체계화되며, 필요에 따라 플로우 전반의 어디에서든 호출된다.

가령, 설계자가 메모리 BIST, EDT, IJTAG 등을 삽입한 특정 프로젝트를 위한 데이터베이스를 생성할 경우 다음 단계에 필요한 다양한 구성요소, 기기, 패턴 및 정보가 서브디렉토리에 의미 있는 이름과 구조를 가지고 저장된다. 데이터베이스 설정은 그림 3과 같다.

설계자의 의도를 포착하는 상위수준의 DFT 사양은 네트워크에서 시작되는데, 이는 IJTAG 규격을 준수하는 칩 내 자원들을 접근 및 제어할 수 있도록 하기 위해서다.

이 사양은 메모리 BIST의 삽입(유형, 번호, 그룹화, 위치)과 스캔 삽입(EDT 컨트롤러의 수와 유형, 컨트롤러당 체인, 위치)을 위한 지침을 제공한다. 아울러 클럭킹 제어, 전력 및 커스텀 DFT 신호를 관리하고, 모든 설정에 오류가 없는지 확인한다. 심지어는 물리적 설계 사인오프에 필요한 SDC 파일까지도 생성할 수 있다.

글: 제이 자한기리(Jay Jahangiri) / DFT 솔루션 부문 매니저 / 지멘스EDA

관련기사

- 반도체 엔지니어 주목, “DFT 자동화의 물결에 주목하라” ①

- 지멘스EDA, 프랙틀테크놀로지스 인수작업 완료…IP검증 제품군 확장

- 2030년 1조달러 반도체 시장, “실리콘(Chip) 아닌 시스템 최적화 설계 고려해야”

- “7나노(nm) 버샬 ACAP, GPU나 ASSP와 전혀 다른 DSA 특화 실리콘”

- IAR시스템즈, 日 덴소 자회사 ‘엔시텍스’와 RISC-V 코어개발 ‘맞손’

- 실리콘아츠, 리스크-V(RISC-V) 기반 GPGPU 설계자산(IP) ‘레이브’ 공개

- 자일링스, 전자설계자동화(EDA) 툴 ‘비바도 ML 에디션’ 출시

- 英 그래프코어 IPU, NHN 광주 데이터센터에 도입된다

- 반도체 디자인하우스 세미파이브, ARM 에코시스템 합류

- 반도체 엔지니어 주목, “DFT 자동화의 물결에 주목하라” ③